Divyansh Manocha

Electronic and Information (MEng) Engineering

Imperial College London

divyanshmanocha [AT] gmail [DOT] com

MIPS 1 CPU Simulator

Built in C++

Project Specification

Implemented the instruction set architecture of MIPS 1, creating a MIPS emulator from scratch with 53 instructions.

Unit testing used for each instruction and test cases to ensure functionality.

A widely used equivalent to the emulator would be qemu-mips.

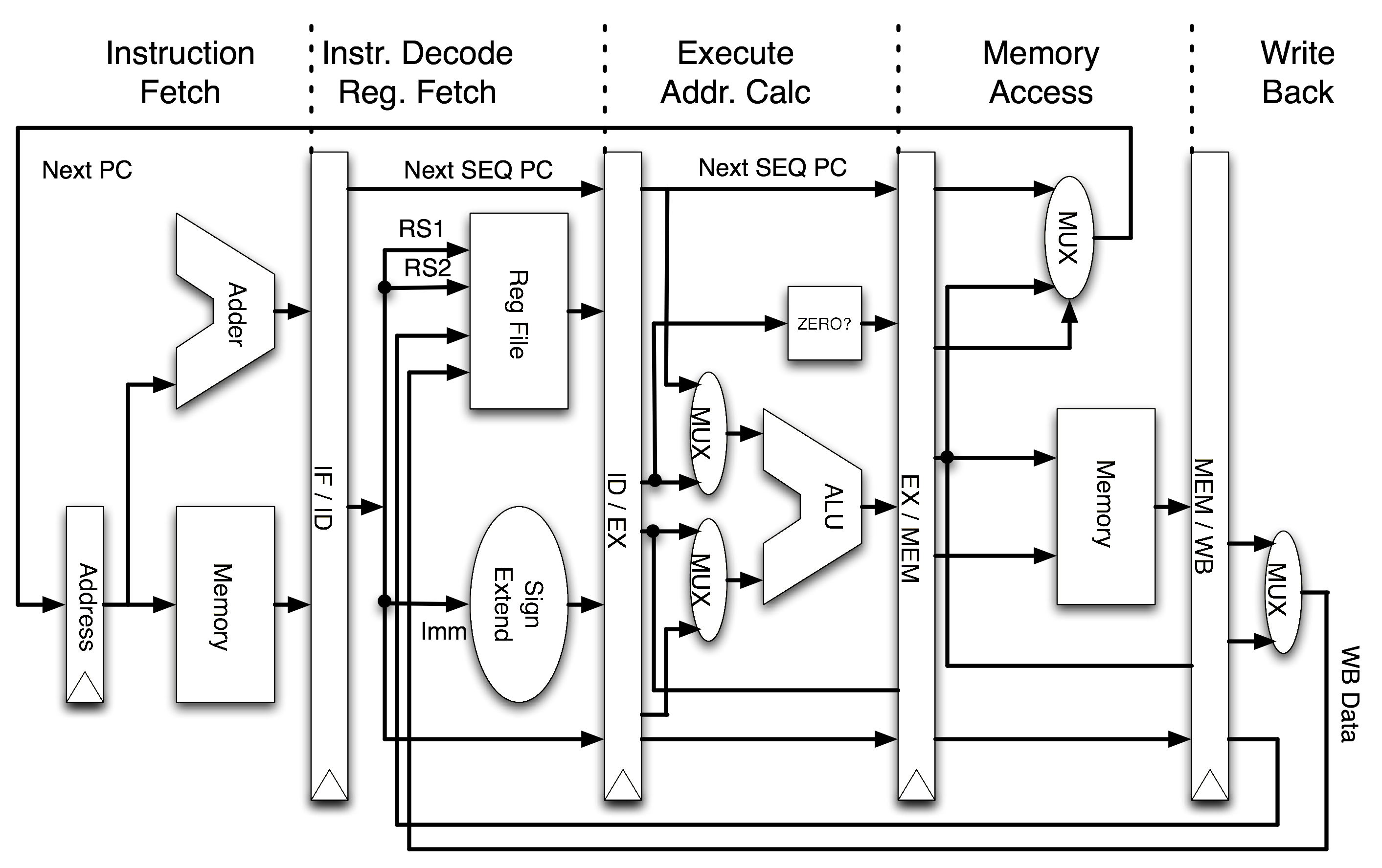

MIPS architecture

Approach

The API involves a context class and memory class. Each class can thereafter generate their own code, without considering other classes.

Context is used to keep track of the scoping, as well as mapping of the variable. The context knows the current scope, and therefore all the declarations within the scope and above it; essentially forming a separate symbol table for each scope. The index of the vector corresponds to the current scope, and the vectors in the structs store the bindings. Subroutines can be called from the context class, as it keeps track of the current function. Allocation of appropriate amounts of memory is evaluated using a separate member function.

Registers and stack allocation are handled by a separate class, passed in the same way as the context. A vector of pointers to structs (that have their own vector) is used for this purpose, with the current value being a string (as they do not have to be initialised). This allows the obtaining of free space (as stack or registers), writing to it, and freeing it as and when necessary. Whether or not a register or the stack is required depends on the member function using it.

Project Outcomes

Compilation: The compiler should be built using: make bin/c_compiler The target environment is Ubuntu 16.04. A test framework was also created for the compiler.

Supported Features

This was definetely a project that improved my abilities as a programmer, as well as helping to better understand the workings of Reduced Instruction Set Architectures.

GitHub link: https://github.com/divyanshmanocha/Mips_CPU